|

ニュース解説

エンタープライズ重視のIntelを示したIDF Spring 2002

2. サーバ向けプロセッサの動向

元麻布春男

2002/03/12

|

|

進化を続けるItaniumファミリ

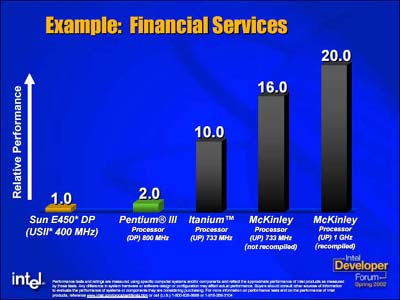

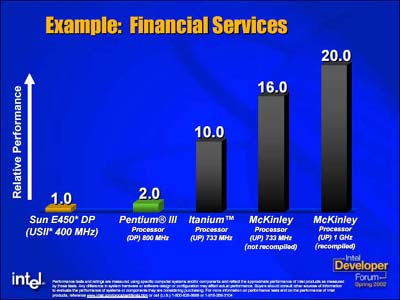

一方、Itaniumファミリについてだが、フィスター副社長のキーノートで力点が置かれたのは、2002年夏に登場する開発コード名「McKinley(マッキンリー)」の性能の高さと、今後もIntelはItaniumファミリのロードマップを更新し続ける、という2点だ。McKinleyは、オン・ダイで3Mbytesの3次キャッシュを実装し、実行ユニットの拡張なども行われている。これによりMcKinleyの性能は、最大で現行のItanium(Merced:マーセド)の2倍に達するという(図3)。

|

| 図3 McKinleyシステムの性能比較 |

| 同じ動作クロック(733MHz)で、同じバイナリ(McKinley用に再コンパイルしていない)のプログラムを実行した場合の性能は、現行のItanium(Merced)の1.6倍になる。動作クロック1GHzのMcKinleyで再コンパイルしたバイナリを用いた場合は、さらに性能が向上し、動作クロック733MHzのItaniumの2倍になるという。

|

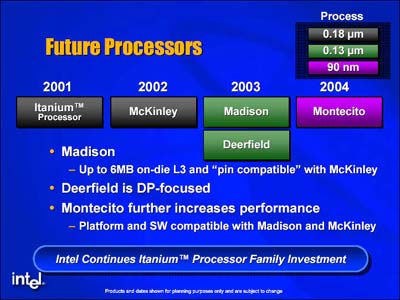

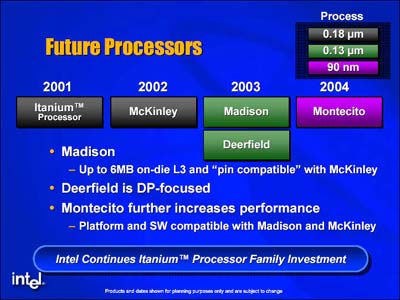

また、将来のItaniumファミリについては、図4のようなロードマップが提示された。2003年には0.13μmプロセスによる開発コード名「Madison(マディソン)」と「Deerfield(ディアフィールド)」で呼ばれるプロセッサが登場する。MadisonがMcKinleyとピン互換の後継プロセッサ(4プロセッサ以上のマルチプロセッサ構成をサポート)として最大6Mbytesの3次キャッシュを搭載する。それに対し、Deerfieldはデュアルプロセッサ構成に特化した、いわば廉価版のプロセッサとなる。デュアルプロセッサ対応のIntel Xeon(Prestonia)の一部を置き換える用途も視野に入れている。2004年には、90nmプロセス(0.09μmプロセス)によるMontecito(モンテシート)が投入される予定だが、MadisonやMcKinleyとの互換性が継承されることになっている。なお、Intel Xeonの直接の後継としてはIA-32に準拠した開発コード名「Nocona(ノコーナ)」と呼ばれるプロセッサが、Deerfieldと同時期に提供される予定だ。

|

| 図4 Itaniumファミリのロードマップ |

| フィスター副社長のキーノートで示されたItaniumファミリのロードマップ。2003年には0.13μmプロセス製造によるMadisonとDeerfieldが投入される。Deerfieldでは、デュアルプロセッサにフォーカスし、ミドルレンジのサーバやワークステーション、ハイエンド・クライアントPCもターゲットにする。

|

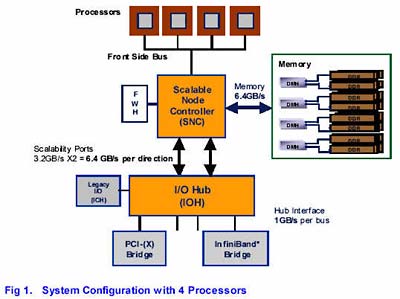

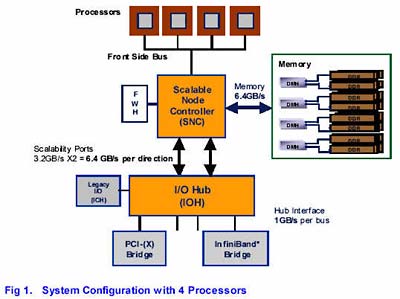

このItaniumファミリに対応したチップセットとして、今回「Intel 870」の概要について情報が公開された。図5は、最小構成のIntel 870システムの例だが、MCH(ノースブリッジ)チップのところにScalable Node Controller(SNC)と呼ばれるチップがある。SNCは、最大4プロセッサをサポートするIntel 870チップセットの中核とでも呼べるチップで、内蔵するメモリ・コントローラは、4つのメモリ・チャンネルを備える。それぞれのチャンネルは1.6Gbytes/sの帯域を持ち、ポイント・ツー・ポイントのリンクにより、DDR Memory Hub(DMH)と接続される(SNCとメモリ間の帯域は6.4Gbytes/s)。DMHのそれぞれが8本のDIMM(PC1600 DIMM)をサポートするため、1つのSNCに32本のDIMMが接続可能ということになる(SNC当りの最大メモリ容量は128Gbytes)。なお、SNCに直接ファームウェア・ハブ(BIOSが実装されたフラッシュメモリ:図ではFWHと記されている)が接続可能な点も、現在のMCHとは異なる部分だ。

|

| 図5 Intel 870チップセットによる構成 |

| プロセッサは2個から実装可能で、ファームウェア・ハブがSNCに直接接続されるようになっている。

|

I/O Hub(IOH)は、4チャンネルのHubLink 2.0インターフェイス(チャンネル当たり1066Mbytes/s)と、ICHを接続するHubink 1.5インターフェイスを備える。Hubink 2.0インターフェイスの先には、P64H2やInfiniBandブリッジ・チップを接続する。SNCとIOHの間は、HubLinkではなく、Scalability Port(SP)と呼ばれるインターフェイスで接続される。SPは40bit幅のポイント・ツー・ポイントのインターフェイスで、うち32bitがデータの転送に用いられる。SPの帯域は、一方向当たり3.2Gbytes/sで、双方向では6.4Gbytes/sとなる。

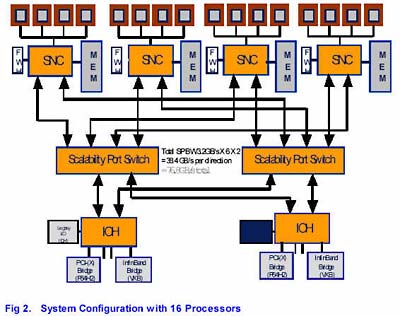

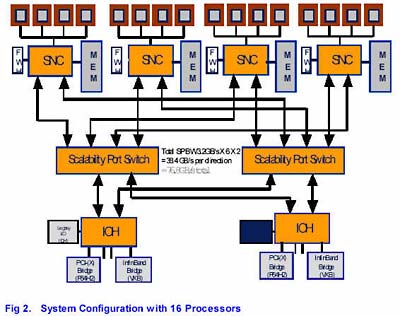

このSPがIntel 870チップセットのスケーラビリティを支える中核技術となる。スイッチ(SPS:Scalability Port Switch)を介することで、複数のSNCを結合し、最大16プロセッサ構成のサーバを構築可能だ(Intelが提供するSPSを使った場合。サードパーティが独自にスイッチを開発することで、16プロセッサ以上のサーバを構築することも可能)。複数のSNCを持つシステムの場合、SNCごとにパーティショニング*1を行い、冗長性を持たせることもできる。ファームウェア・ハブがSNCに接続できるようになっているのは、このようにパーティショニングを可能にするためでもある。

| *1 パーティショニングとは、サーバ・マシンの能力を分割する機能のこと。分割されたそれぞれのパーティションは、ソフトウェアから見ると別々のサーバとして機能し、例えば各パーティションで別々のOSを実行したり、クラスタ構成にして冗長化したり、といったことが可能になる。本稿におけるパーティショニングは、SNCというハードウェアの単位で分割する物理パーティショニング(ハードウェア・パーティショニング)である。 |

4つのSNCを結合した図6の場合、最大メモリ容量は4倍の512Gbytesとなるが、メモリはそれぞれのプロセッサから、最大512Gbytesのリニアなメモリ空間として見える。このような構成においては、ローカル・メモリ(メモリ・アクセスを行うプロセッサが接続されているSNCに接続されたメモリ)と、リモート・メモリ(メモリ・アクセスを行うプロセッサが接続されているのとは、別のSNCに接続されたメモリ)で、メモリ・アクセスのレイテンシ(遅延時間)が著しく異なることになる。そこでIntel 870のSNCには、頻繁に利用するメモリがローカルとリモートのどちらにあるかを調べることができるよう、ホット・ページ(Hot Page)と呼ばれる仕組みが備わっている。プログラマは、ホット・ページを利用することで、頻繁に利用するメモリがローカルなのかリモートであるかを識別し、必要に応じてそれをローカルにコピーすることで、メモリ・アクセスの最適化を行うことが可能だ。

|

| 図6 Intel 870チップセットを用いた16プロセッサ構成 |

| Scalability Port Switch(SPS)により、4つのSNCが結合されている。SPSの設定により、SNCごとにパーティショニングを行い、内部でクラスタリング構成にすることも可能だ。

|

IA-32プロセッサの64bit化を検討中?

こうしたエンタープライズ関連の発表から伝わってくることは、IntelがItaniumファミリに対して強くコミットしている、ということだ。IDFの直前、一部の新聞にIntelが「Yamhill(ヤムヒル)」の開発コード名で呼ばれる技術を準備中であるとの記事が出た。その記事によるとYamhillは、将来のIA-32プロセッサであるPrescottに密かに内蔵しようとしている技術で、AMDのx86-64アーキテクチャのように、32bitアーキテクチャと64bitアーキテクチャを1つのプロセッサ・アーキテクチャに内蔵させようというものだという。Presocttのリリース当初からYamhillを有効にする予定はないが、もしAMDのx86-64アーキテクチャを実装したプロセッサ「Hammer(開発コード名:ハマー)」に遅れをとるような事態が生じれば、Yamhillを有効にすることでIntelは対抗する、といった内容である。

すでに64bitアーキテクチャのItaniumが存在しているにもかかわらず、こうした記事が出るということ自体、現在のItaniumが必ずしも順調でないこと(性能的にも、ビジネス的にも)の証といえるだろう。今回のIDFにおけるフィスター氏のキーノートは、第2世代のItaniumファミリであるMcKinleyによる性能の飛躍的な向上と、将来に渡るロードマップを提示することで、Itaniumファミリに関するIntelのスタンスに何ら揺るぎがないことを示す意図があった、と考えられる。かといってYamhillを完全に否定するものでもないが、Itaniumファミリに対する力の入れ具合を感じた。

System Insider フォーラム 新着記事

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう

- 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は?

- IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか?

- スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

System Insider 記事ランキング

本日

月間