“世界最速の組み込み向けプロセッサ”

64コアCPU「TILE64」を提供開始、MITのスピンアウト

2007/08/21

マサチューセッツ工科大学出身者が2004年に創業したベンチャー企業、米Tileraは8月20日(現地時間)、64個のコアからなるプロセッサ「TILE64」を発表した。価格は1万個出荷時435ドルから。また、同社は今後、36コア、120コアの製品も予定している。

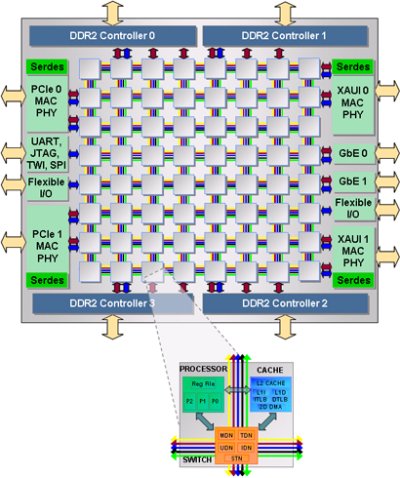

通常、コア間を結ぶバスの代わりに、同社が“iMesh”と呼ぶメッシュ状の通信経路をダイ上で2次元の格子状に確保。各コアにはスイッチを付けてパケットをルーティングする。各コアにはL1、L2キャッシュが付属するほか、L3キャッシュはiMeshに分散して配置されているという。また、4つのDDR2メモリコントローラ、2つの10Gbpsのネットワーク、2つの10Gbps対応PCIe、2つのギガビットイーサネットワーク、プログラマブルI/Oなどのインターフェイスを持つ。TILE64の動作クロックはモデルにより600〜900MHz。

こうした新しいアーキテクチャにより、従来コア数が増えるに従ってコア間通信の“渋滞”が起こっていたものが解消される。同社はiMesh技術により、数百コア、数千コア程度にまでスケール可能だとしている。同社は発表文の中で、従来のマルチコア化の技術を「中心に交差点がある古い都市」にたとえている。これは自転車の車輪のスポークのようなもので、すべてのコアの通信が必ず中心を通るために渋滞が起こる。一方、iMeshは整然と区画整理された「近代的な都市の道路」のようだという。

TILE64のターゲットはネットワーク機器やデジタル家電への組み込み。1チップでレイヤ4〜7のセキュリティアプライアンスであれば20Gbpsのスループット、映像関連製品であればH.264のHD映像を2本分エンコードする、きわめて高い能力を持つという。

各コアはLinuxを稼働できる。同社は、1ワット当たりのパフォーマンスでは、インテルのデュアルコアXeonの10〜30倍、またテキサス・インスツルメンツのDSPの40倍の性能だとしている。

並列処理向けの開発環境として、Eclipseベースの「MDE」(Muticore Development Environment)をオープンソースのコードとして提供する。グラフィカルなUIで、マルチコア処理のプロファイリングやデバッグが可能。

関連リンク

関連記事

情報をお寄せください:

最新記事

|

|