|

解説

IDF Spring 2003レポート(1) 2. シリアルへと向かうサーバI/Oのロードマップ 元麻布春男 |

|

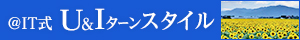

一方、4ウェイ以上のマルチプロセッサと大容量の3次キャッシュを備えたIntel Xeon MPは、一般にPentium 4やIntel Xeonとリリース時期が異なる。製造プロセスにしても、一定期間遅れて適用されている(動作クロックも低い)。デスクトップPC向けの1カ月後にDP版が出て、その半年後にMP版といったスケジュールは珍しくない。ここでも開発コード名「Potomac(ポトマック)」で呼ばれる次期コアのリリース時期は、Noconaに比べて1年近く遅れる(図5)。大容量の3次キャッシュの搭載による製造上の問題だけでなく、このクラスのプロセッサとなると、より慎重な動作検証などが求められるからだろう。リリース時期のギャップを埋めるかのように、3次キャッシュを4Mbytesに増量することで性能向上を図ったIntel Xeon MP(Gallatin)が2004年前半リリースされる予定となっている。

|

| 図5 Intel Xeon MPのロードマップ |

| Intel Xeonに対して、時系列が後ろにずれていることに注意したい。このクラスのプロセッサでは、動作検証に時間がかかることや、サーバ・ベンダが矢継ぎ早のプロセッサ・リリースを好まないことから、やや製品の間隔が長い。 |

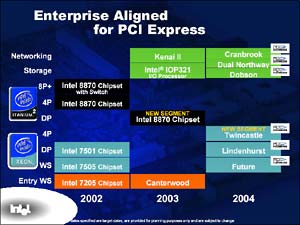

図5で注目したいのは、Potomacの下に「New Platform(新プラットフォーム)」の文字があることだ。つまり、ここで新しいチップセットが投入される。これまでIntel Xeon MPのチップセットは、ServerWorksなどのサードパーティに依存してきた。Intelは、Potomacの投入と同時に、新しくこのクラスに対して開発コード名「Twincastle(ツインキャッスル)」と呼ぶチップセットを投入する予定だ。図6がそのロードマップだが、2004年に登場するIntel Xeon用チップセット「Lindenhurst(開発コード名:リンデンハースト)」を含め、すべてがPCI Express対応となる。また同時に、メモリにはDDR IIが採用されることになっている。

このようにサーバ向けのIA-32プロセッサも、順調に性能が引き上げられていく予定だ。IPFの攻勢とともに、Intelがサーバ向けプロセッサ市場においても独占に近いシェアを獲得する日も近いかもしれない。

クラスタリングかマルチプロセッサかの議論に対する回答

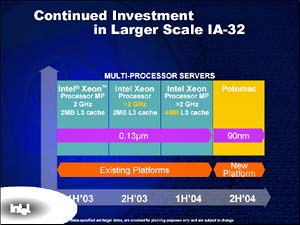

Intel XeonとIntel Xeon MPで、よく話題になるのがIntel Xeonのデュアル構成のシステム2台をクラスタリングした場合と、Intel Xeon MPの4ウェイ・システムのどちらが高い性能を発揮するか、ということだ。上述したようにIntel Xeon MPは大容量の3次キャッシュを持つ代わりに、動作クロックそのものはIntel Xeonよりも低い。プロセッサの数が同じ4個で、性能があまり変わらないのであれば、だれしもが安価なIntel Xeonを使いたいと考えるだろう。今回のIDFでは、フィスター上級副社長のキーノート・スピーチの中に、この比較を行うデモがあったほか、大容量キャッシュを搭載したIntel Xeon MPのメリットを紹介するセッションが用意された(図7)。こうしたデモを披露したのは、Intel Xeon MPを拡販したいという意識の表れかもしれない。

|

| 図7 Amazon.comによるケーススタディ |

| オンライン書店であるAmazon.comのOracle 9i RACを用いたケーススタディ。ワークロードによっては異なる結果が得られることもあるのだろうが、この場合は同じ4個のプロセッサでもIntel Xeon MPシステム(1.60GHz)がIntel Xeonシステム(2.40GHz)のクラスタリングを上回っていた。 |

Pentium-Mのサーバ展開は?

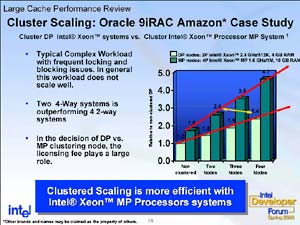

さて、サーバ向けのIA-32プロセッサでありながら、ここまで触れてこなかった製品が1つある。それは、開発コード名「Banias(バニアス)」改め、Pentium-Mという名称になったプロセッサだ。現在、製品の扱いが通信事業者向け製品を担当するICG(Intel Communication Group)に移管されたため、サーバ向けのプロセッサとしては傍流(?)になってしまった感がある。そのPentium-Mを、展示会場のひょんなところで見かけた(写真2)。通信業界向けサーバのプロセッサ・モジュールに実装されており、しかもチップセットにIntel Xeon対応のIntel E7501が採用されていた。この組み合わせについてたずねたところ、「Intel E7501には一切手を加えていない(Pentium-M用の改修は施していない)」ということで、Pentium-Mの外部バスが少なくとも論理的にはPentium 4やIntel Xeonと変わらないことが判明した(バスの駆動電圧は変わっている可能性が高い)。ただし、Pentium-Mはデュアルプロセッサ構成のサポートはできないということである。

|

| 写真2 Pentium-Mを用いたプロセッサ・モジュール |

| Pentium-Mを採用した通信業界向けサーバのプロセッサ・モジュール。チップセットには、Intel Xeon用のIntel E7501が採用されていた。 |

シリアルへ向かうI/O

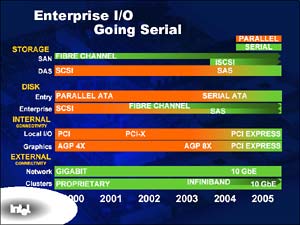

チップセットのPCI Express対応でも分かるとおり、2004年以降、I/Oの分野にも大きな変革が訪れる。それは、シリアル化の波だ。図8はFister副社長のキーノートからとったものだが、オレンジ(パラレル・インターフェイス)が消え、緑(シリアル・インターフェイス)で置き換えられていることが良く分かる。その中核となるのがPCI Expressだ。今回のIDFに合わせて、PCI Expressに接続するPCI-Xブリッジの仕様が規格化されるなど、デスクトップPCにとどまらず、文字通りPCIの後継として広く使われることを目指して、開発が進められている。

|

| 図8 サーバI/Oの変移 |

| サーバI/Oにもシリアル化の波が押し寄せる。2004年にはストレージ分野のシリアル化が本格化する。 |

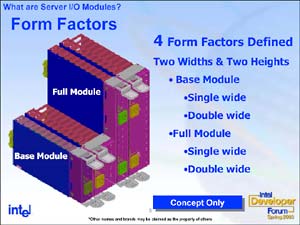

PCI Expressは、単に広い帯域を安価に得られるだけでなく、サーバで求められる高信頼性の確保や、ホットプラグにも対応する。また、PCI Expressを利用して、サーバをモジュール化する試みもなされている(図9)。PCI Expressが、デスクトップPC同様、サーバにも大きなインパクトを与えることが期待される。ただ、全機能を利用するにはOSのサポートが必要なこと、Intelとサードパーティで開発に対する温度差があるように思える点が若干気にかかる。特にOSのサポートについては、PCI ExpressがPCIバスのソフトウェア・モデルで動作は可能なものの、それだけでは全機能が利用できないことから、早急な対応が望まれる。チップセットのリリースが始まる2004年には、OSの対応状況など、PCI Expressに関する話題がさらに増えることになるだろう。

|

| 図9 PCI Expressによるサーバのモジュール化の試み |

| PCI Expressを用いたモジュールでも、モバイルPCや省スペース・デスクトップPC向けの「NEWCARD(PCカードの後継規格)」がPCMCIAにより規格化されるのに対し、こちらはそこまで具体化していない。 |

同じく2004年から本格化すると期待されているのがストレージ・インターフェイスのシリアル化だ。デスクトップPC向けには、今年登場するCanterwood(開発コード名:キャンターウッド)やSpringdale(同:スプリングデール)といったチップセットにシリアルATAに対応したサウスブリッジ(ICH5/ICH5R)が採用される。なお、Canterwoodは、図6にあるようにエントリ・クラスのワークステーションにも採用される。こうした動きは、2004年にサーバへも波及するだろう。

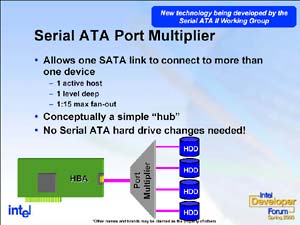

現在、シリアルATAをサーバ向けに拡張するシリアルATA IIフェイズ1が標準化作業中だが、すでに明らかになっているコマンド・キューイングのサポートに加え、今回のIDFでは幾つかの追加拡張が明らかになった。図10は、1つのポートに複数のハードディスクを接続可能にする「ハブ」となるシリアルATAポート・マルチプライヤーのアイデアだ。これにより、サーバに求められるストレージ容量の確保や、RAID構成のサポート(ソフトウェアRAIDを含めて)が容易になると思われる。また、シリアルATAフェイル・オーバーと呼ばれる機能は、1台のドライブに2つのホスト・コントローラを接続しておき、片方を待機状態にしておくことで、ホスト・コントローラにも冗長性を持たせようというアイデアである。

|

| 図10 シリアルATAポート・マルチプライヤーの概要 |

| シリアルATAポート・マルチプライヤー(Serial ATA Port Multiplier)を採用することで、1つのシリアルATAポートに複数のハードディスクを接続可能にしようというアイデア。ただし、複数のマルチプライヤー(ハブ)を階層化して接続することは考えられていない。 |

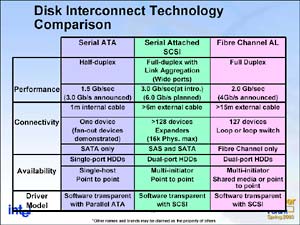

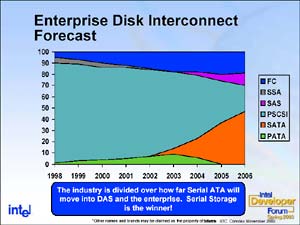

このシリアルATA IIに触発されるように、現在標準化が進められているもう1つのシリアル・インターフェイスがSerial Attached SCSI(SAS)である。シリアルATAがパラレルATAとソフトウェア互換性を持つように、SASは既存のSCSI対応ソフトウェアの資産活用が狙いだ。従ってシリアルATAに比べて接続可能なデバイス数が多いほか、最大ケーブル長も長い(図11)。また、シリアルATAと上位互換性を持つのも特徴の1つで、SASのホスト・アダプタにはシリアルATAのハードディスクを接続することもできる(逆は不可)。こうしたディスク・インターフェイスのシリアル化により、2005年には、サーバ向けディスクの大半がシリアル・インターフェイス対応になると予想されている(図12)。

|

| 図11 シリアルATA、SAS、Fibre Channel ALの比較 |

|

| 図12 サーバ向けハードディスクのインターフェイス別シェア予測 |

| インターフェイスのシリアル化は2003年から本格化し、2005年には大半を占めるようになると見られている。 |

IAサーバも液冷へと向かうのか?

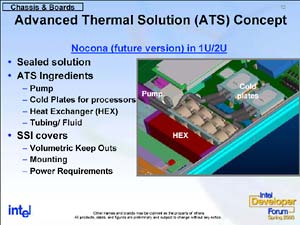

サーバ関連のそのほかの話題としては、プロセッサの冷却にいよいよ液冷が真剣に検討されていることを挙げておきたい。液冷というと日立製作所がノートPCに採用して話題を呼んだが、今回はIntel自身が、Noconaの後継プロセッサを用いたデュアルプロセッサ・サーバの冷却に液冷システムの採用する計画があることを明らかにした(図13)。だが、「本家」である日立製作所は、すでに液冷システムを用いたブレード・サーバのコンセプト・モデルを展示会場でデモしていた。コンセプト・モデルといっても、自動閉鎖弁を用いるなどして、ポンプ・ユニットやサーバ・ブレードのホットスワップにも対応したもので、一歩先を行っていることをアピールしていた。

|

| 図13 サーバに採用を検討中の液冷システム |

| Noconaの将来版を用いた1U/2Uサイズのラックマウント型サーバに対し、液冷システム(Advanced Thermal Solution)の適用を検討している。 |

今回は、IDF Spring 2003におけるサーバ関連の話題を紹介した。次回は、IDF Spring 2003で公開された、2003年後半のクライアントPCの概要について解説する。![]()

| INDEX | ||

| IDF Spring 2003レポート | ||

| 市場完全制覇への階段を登るIntelのサーバ・プロセッサ戦略 | ||

| 1.2005年までのプラットフォーム互換を保証したItaniumプロセッサ・ファミリ | ||

| 2.シリアルへと向かうサーバI/Oのロードマップ | ||

| 「System Insiderの解説」 |

- Intelと互換プロセッサとの戦いの歴史を振り返る (2017/6/28)

Intelのx86が誕生して約40年たつという。x86プロセッサは、互換プロセッサとの戦いでもあった。その歴史を簡単に振り返ってみよう - 第204回 人工知能がFPGAに恋する理由 (2017/5/25)

最近、人工知能(AI)のアクセラレータとしてFPGAを活用する動きがある。なぜCPUやGPUに加えて、FPGAが人工知能に活用されるのだろうか。その理由は? - IoT実用化への号砲は鳴った (2017/4/27)

スタートの号砲が鳴ったようだ。多くのベンダーからIoTを使った実証実験の発表が相次いでいる。あと半年もすれば、実用化へのゴールも見えてくるのだろうか? - スパコンの新しい潮流は人工知能にあり? (2017/3/29)

スパコン関連の発表が続いている。多くが「人工知能」をターゲットにしているようだ。人工知能向けのスパコンとはどのようなものなのか、最近の発表から見ていこう

|

|