製造プロセス、アーキテクチャを交互に進化

「ムーアの法則」に続くインテル「チックタックモデル」とは?

2007/09/28

インテルは9月28日会見し、11月に出荷開始する予定の新クアッドコアプロセッサ「Xeon 5400番台」をデモンストレーションした。今後10〜15年でムーアの法則が限界を迎えるとの指摘もある中、インテルは最近、チックタックモデルと呼ぶ新しいプロセッサの開発モデルを採用している。会見した米インテルの上席副社長 パット・ゲルシンガー(Patrick P. Gelsinger)氏はチックタックモデルに基づく、今後のロードマップを明らかにした。

米インテルの上席副社長 パット・ゲルシンガー氏

米インテルの上席副社長 パット・ゲルシンガー氏チックタックモデルとは、CPUの製造プロセスとアーキテクチャを1年ごとに交互に進化させていくモデル。2007年は45ナノの開発プロセスで製造するプロセッサファミリ「Penryn」(コード名)を導入。アーキテクチャは従来の「インテル Core マイクロアーキテクチャー」を採用する。2008年は、開発プロセスは45ナノのままだが、アーキテクチャを進化させる。そのプロセッサファミリはコード名で「Nehalem」と呼んでいる。

チックタックモデルでは、製造プロセス、アーキテクチャとも寿命は2年。しかし、それぞれの進化のタイミングをずらすことで、急激な変化によるリスクを低減し、ユーザーがシステム資産を長く使えるようにする狙いがある。ゲルシンガー氏は「ムーアの法則を実現する製品リリースだ」としている。チックタックモデルによれば、インテルは2009年にNehalemと同じアーキテクチャを採用し、製造プロセスを32ナノに進化させた「Westmere」を出荷。2010年は32ナノプロセスで新しいアーキテクチャを採用した「Sandy Bridge」と開発する計画だ。

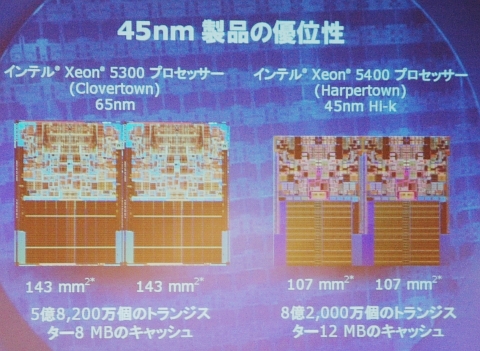

45ナノプロセスで開発する初のプロセッサであるXeon 5400番台(コード名:Harpertown)は、65ナノで製造するXeon 5300番台と比べて、ダイサイズを小さくしたにもかかわらず、トランジスタ数を5億8200万個から8億2000万個に増やした。業界初のHigk-K(高誘電率)ゲート絶縁膜と金属ゲートを採用し、トランジスタの集積度やトランジスタスイッチング速度を向上させた。Xeon 5300番台と比べると、Xeon 5400番台はJavaアプリケーションの処理で25%向上。ワークステーションのマルチタスク処理では23%アップするという。

Xeon 5300番台と5400番台との比較

Xeon 5300番台と5400番台との比較関連リンク

関連記事

情報をお寄せください:

最新記事

|

|